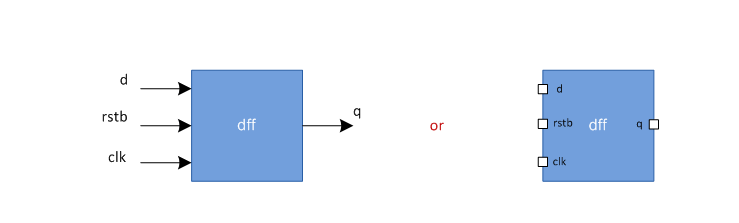

모듈이란 무엇입니까?

모듈은 Verilog HDL로 설계된 기본 단위입니다.

모듈은 입력, 출력 및 회로 작업을 포함할 수 있는 독립적인 하드웨어 구성 요소입니다.

다른 모듈의 모듈 인스턴스화 아마도.

인스턴스란 무엇입니까?

인스턴스는 Verilog HDL에서 모듈을 사용하는 방법입니다.

인스턴스는 모듈을 복사하여 구현되는 하드웨어 구성 요소를 의미합니다.

모듈 인스턴스는 원래 모듈과 동일한 기능을 수행하지만 모듈과 달리 구현된 실제 하드웨어를 나타냅니다.

다음모듈과 인스턴스를 사용하여 간단한 2:1 멀티플렉서를 구현하는 Verilog의 HDL 코드 샘플입니다.

// 2:1 멀티플렉서 모듈 정의

module mux2to1(

input a, b, sel,

output y

);

assign y = sel ? b : a;

endmodule

// 2개의 2:1 멀티플렉서를 사용하여 4:1 멀티플렉서 구현

module mux4to1(

input (3:0) data_in,

input (1:0) sel,

output reg y

);

wire (1:0) sel1;

wire (1:0) sel2;

wire y1;

wire y2;

// 하위 멀티플렉서 인스턴스 생성

mux2to1 mux1(.a(data_in(0)), .b(data_in(1)), .sel(sel1(0)), .y(y1));

mux2to1 mux2(.a(data_in(2)), .b(data_in(3)), .sel(sel1(0)), .y(y2));

// 상위 멀티플렉서 동작

always @(sel or sel1 or sel2 or y1 or y2) begin

sel1(0) = sel(0);

sel1(1) = sel(0);

sel2(0) = sel(1);

sel2(1) = sel(1);

mux1.sel = sel1(1);

mux2.sel = sel2(1);

if(sel1 == 2'b00) y <= y1;

else if(sel2 == 2'b00) y <= y2;

else y <= 1'bx;

end

endmodule

위의 샘플 코드에서 mux2to12:1 멀티플렉서를 나타내는 모듈이며, mux4to1두 mux2to1 4:1 멀티플렉서를 구현하기 위해 모듈을 인스턴스화하는 모듈입니다. 모듈과 인스턴스는 Verilog HDL에서 가장 기본적인 빌딩 블록 중 두 가지입니다.

모듈과 인스턴스는 Verilog HDL에서 가장 기본적인 빌딩 블록 중 두 가지입니다.

인스턴스는 모듈의 물리적 사본입니다. 인스턴스에는 모듈의 특정 인스턴스를 식별하는 이름과 해당 모듈에 대한 포트 연결이 있습니다. 인스턴스는 모듈의 코드를 사용하여 테마를 구현하는 데 사용됩니다. 인스턴스는 모듈 인스턴스화 프로세스를 통해 생성됩니다.

예를 들어 위에서 구현한 멀티플렉서 모듈을 사용하여 인스턴스를 만드는 코드는 다음과 같습니다.

module top_module(

input a,

input b,

input sel,

output y

);

// 멀티플렉서 모듈 인스턴스화

mux_2to1 mux_inst(

.a(a),

.b(b),

.sel(sel),

.y(y)

);

endmodule위의 코드에서 mux_inst~이다 mux_2to1 모듈의 인스턴스. 예 mux_inst~이다 ㅏ, 비, 셀 그리고 제이각 포트는 mux_2to1 모듈의 해당 포트에 연결됩니다.

즉, 모듈은 설계의 일부를 구현하는 데 사용되며 인스턴스는 모듈의 물리적 사본입니다. 인스턴스는 모듈의 인스턴스화 프로세스에 의해 생성되며 모듈의 코드를 사용하여 디자인을 구현하는 데 사용됩니다.